三星分享逻辑、DRAM和NAND未来十年的路线图

来源:内容由半导体行业观察(ID:icbank)编译自semiwiki,谢谢。

Kinam Kim 是三星的一位资深技术专家,过去多年来发表了许多优秀的文章。他现在是三星电子的董事长,在 之前举办IEDM 上,他还做了一个非常有趣的主题演讲。

他首先从一些一般性观察开始:

他表示,世界正在经历一场由半导体驱动的变革,由于疫情的影响,加速了对非接触式社会的需求,远程工作和远程教育也在迅速发展,IT 变得必不可少。传感器、处理器和内存都是必需的。这种趋势也让数字化的采用取得了巨大的飞跃。数据显示,远程工作的比例从 25% 增加到 58%。经济数字化带来了巨大的机遇,智能系统正在产生大量数据。

在过去的 50 年里,每片晶圆的晶体管数量增加了 1000 万倍,处理器速度增加了 10 万倍,成本每年下降 47%。半导体与人脑有相似之处,传感器就像眼睛,处理器和内存负责处理和存储。将传感器与处理相结合的智能手机可实现新的应用,

有一个关于传感器的有趣部分,但这并不是我真正的领域,我想专注于他介绍的逻辑、DRAM 和 NAND 路线图。

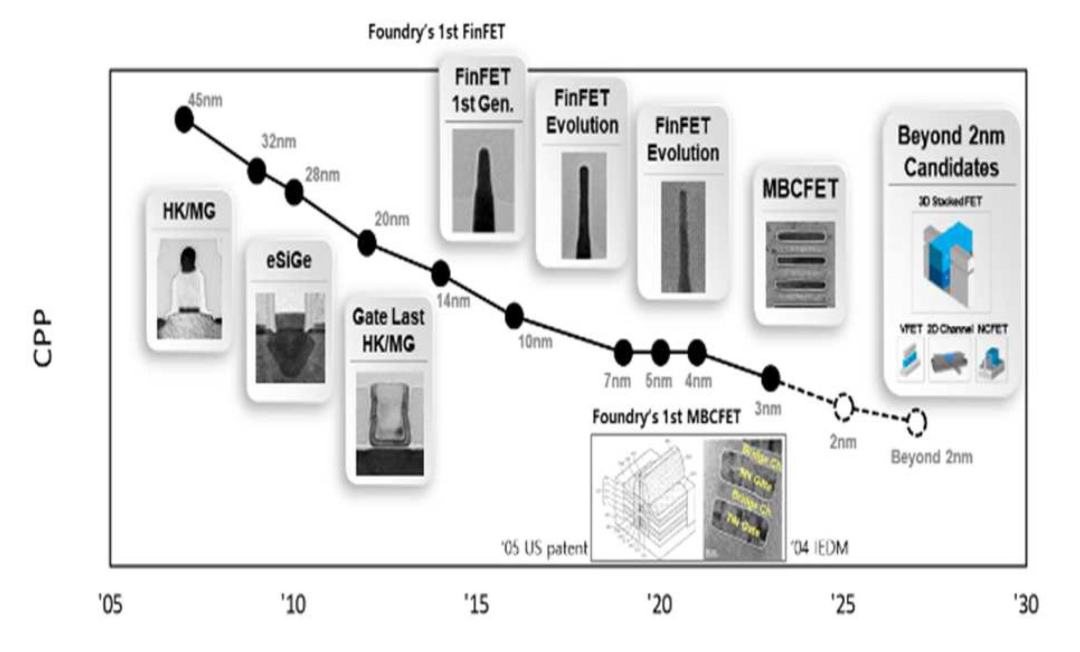

图1. 逻辑路线图。

首先看逻辑方面,在图 1 中,我们可以看到逻辑工艺的接触式多晶硅间距 (contacted poly pitch:CPP) 如何随着时间的推移而扩展。在平面时代,我们看到了英特尔在 45nm 和代工厂推出的 28nm 高 k 金属栅极 (HKMG) 以及嵌入式硅锗 (eSiGe) 等创新技术,以通过应变提高沟道性能。

FinFET 由英特尔在 22nm 推出,并在 14/16nm 被代工厂采用,并在多个节点上推动了行业向前发展。三星目前正试图通过他们称为多桥的水平纳米片 (HNS) 引领行业进入GAA时代,而 HNS 应该为行业带来至少两个节点。在2nm 以后,三星预计 3D 堆叠 FET(其他人称为 CFET 或 3D FET)、IBM 和三星最近披露的 VFET、2D 材料或负电容 FET (NCFET) 中的一种或多种技术会成为候选。

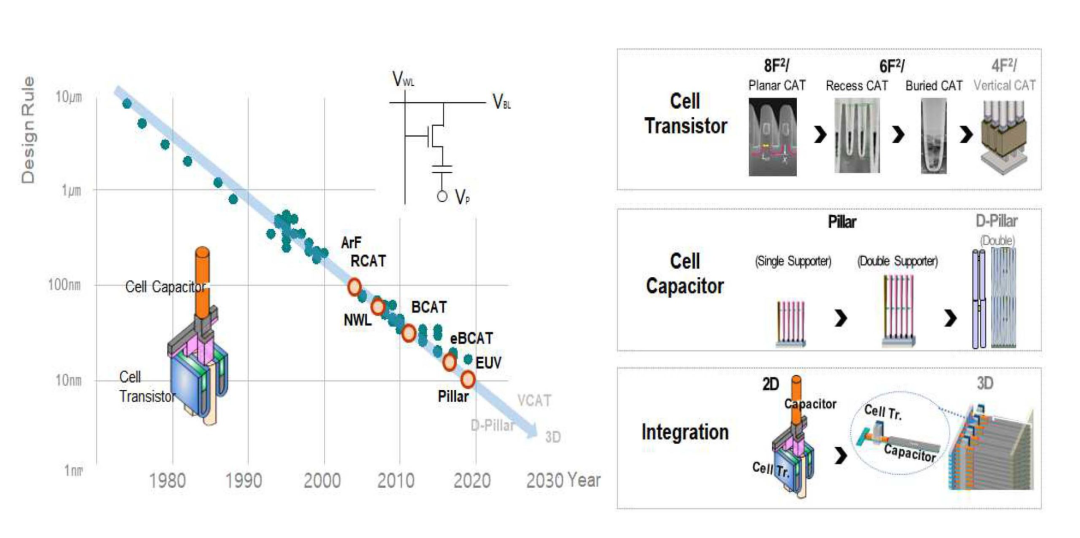

图2.DRAM 路线图

其次,我们看一下三星分享的DRAM路线图。据介绍,随着 EUV 在 DRAM 中的应用,下一个挑战是缩小存储单元。三星预计很快将投入两层电容器。预计在本世纪后期将转向垂直存取晶体管,随后是 3D DRAM。我无法找到有关如何构建 3D DRAM 的更多具体信息,但 ASM、应用材料公司和东京电子公司的演示文稿以及本演示文稿中说明了类似的结构,这表明该行业正在寻求解决方案。

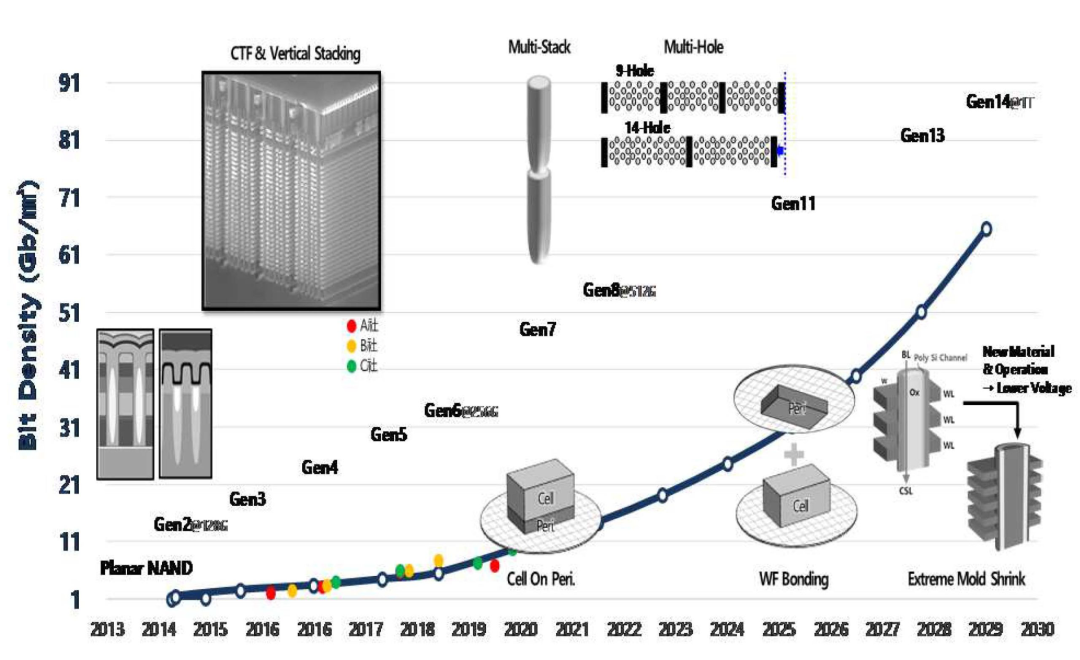

图3.NAND 路线图

最后,三星还分享了NAND的路线图。据了解,三星最新的 3D NAND 是 176 层工艺,第一次使用串栈(对他们来说是第一次串栈(string stacking),别人已经串了好几代了)和第一次使用阵列下的外设设计(对他们来说,其他人已经做了好几代了)。接下来是缩小沟道孔之间的间距以提高密度,同时增加层数。大约在 2025 年,三星将展示晶圆键合以分离外围电路和内存阵列。起初,我对此感到惊讶,首先长江存储已经在这样做,如果三星认为它提供了优势,我很惊讶他们会等这么久才实施它。其次,我对晶圆键合进行了成本建模,我相信它比当前的单片方法成本更高。在考虑了更多之后,我想知道它是否被视为解决允许连续层堆叠的压力问题,并且将在需要继续堆叠时实施。

最后,在这十年的后期,三星预计材料会发生变化,并且通道孔会进一步缩小。这里显示的图没有显示它,但在他们的演示中,三星展示了他们第 14 代工艺的一千多个层。

总之,主题演讲提出了一个观点,即逻辑、DRAM 和 NAND 在本世纪末持续扩展和改进。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2935内容,欢迎关注。

免责声明:上述内容仅代表发帖人个人观点,不构成本平台的任何投资建议。

这个文章关于三星真的不错[开心]

$苹果(AAPL)$ $谷歌A(GOOGL)$ $Meta Platforms(FB)$ $台积电(TSM)$ $ARK Innovation ETF(ARKK)$