Chiplet技术是什么?它有什么存在意义?

Chiplet并不是一个新鲜的概念,台积电和英特尔较早就已经开发了相应的技术,但是早年的技术成本还是较高。“但因为是先进技术,所以有很大的想象空间。”

在机构看来,随着芯片制程的演进,由于设计实现难度更高,流程更加复杂,芯片全流程设计成本大幅增加,“摩尔定律”日趋放缓。在此背景下,Chiplet被业界寄予厚望,或将从另一个维度来延续摩尔定律的“经济效益”。

什么是Chiplet技术?

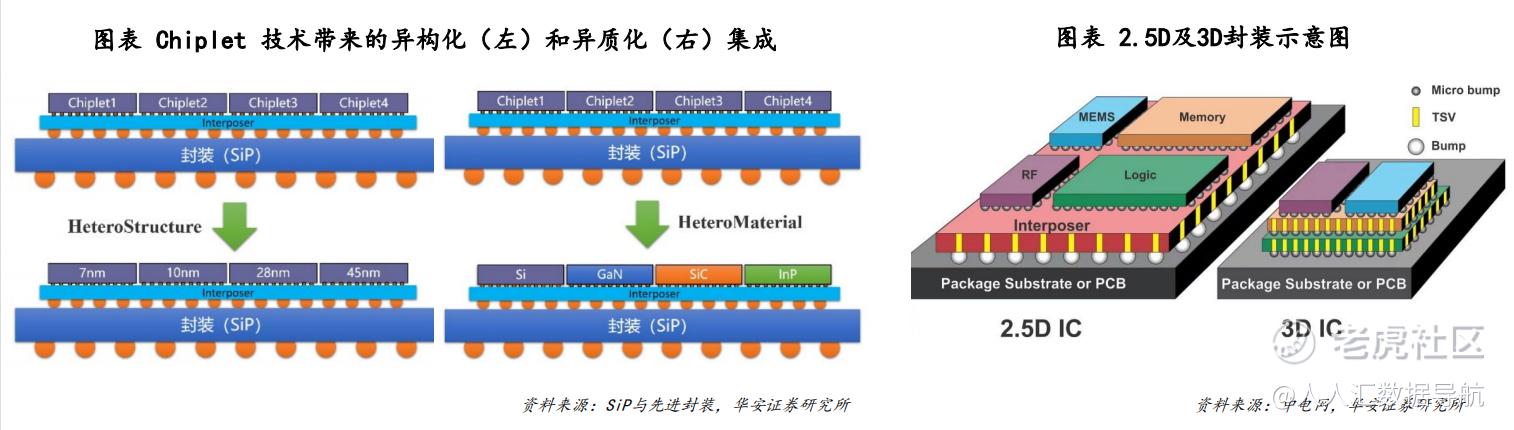

Chiplet通常被翻译为“粒芯”或“小芯片”。单从字面意义上可以理解为更为“粒度更小的芯片”。它是一种在先进制程下提升芯片的集成度,从而在不改变制程的前提下提升算力,并保证芯片制造良品率的一种手段。

现代芯片制造工艺可以被视为一个无限追求摩尔定律极限的过程,而当芯片的工艺制成突破28nm以下时,传统的平面晶体管结构便完全不能支撑进一步的微缩,而业界对此的应对措施当然也很直接——改结构。

2011年初,英特尔推出了一种基于FinFET(鳍式场效应晶体管)的商用芯片,将其使用在22nm节点的工艺上。随后,台积电等半导体代工厂也纷纷开始推出自己的FinFET芯片。到2012年,FinFET的应用已开始向20nm节点和14nm节点推进。

此后为了突破平面晶体管结构的支撑限制,GAAFET技术、MBCFET技术也相继问世,将现代芯片制造一步步推向摩尔定律的极限。可随着工艺制成迈入10nm级别,芯片制造商才真正遇到了让其“头疼”的问题。

不断逼近物理极限的晶体管加工早已让现有的光刻技术“不堪重负”。一味地追求极限地微缩让芯片生产中出现地工艺误差和加工缺陷越来越严重。这反应到产品上便是芯片的成品率下降和器件的故障率升高。对此,传统的解决方案是继续加大投资,改善工艺,加强品控,但物理极限的天花板并不是巨量投资能够突破的。

在这样的背景下,研究人员给出了新的思路,既然缺陷无法避免,那么就想办法将缺陷“击中”的裸芯控制在一个较低的比率上。

换句话说,在缺陷“密度”确定的情况下,裸芯的面积越小,没有被缺陷“击中”的裸芯就越多。所以将大芯片切割成为小芯片(Chiplet)就变成了业界提升芯片良品率的一种选择,或者说是目前为止较好的一种选择。

举例来说,在一颗7nm工艺制程的芯片中,一些次要的模块可以用如22nm的较低的工艺制程做成Chiplet,再“拼装”至7nm芯片上,原理如同搭积木一样,这样可以减少对7nm工艺制程的依赖。Chiplet模式也是在摩尔定律趋缓下的半导体工艺发展方向之一。

海外芯片巨头构建Chiplet标准联盟

到目前为止AMD、英特尔以及台积电等多家国际头部芯片设计企业和多家中国芯片设计企业都曾表明或已经实现在产品中导入 Chiplet 设计。

据公开资料显示,华为于2019年推出了基于Chiplet技术的7nm鲲鹏920处理器。AMD今年3月推出了基于台积电3D Chiplet封装技术的第三代服务器处理芯片,苹果则推出了采用台积电CoWos-S桥接工艺的M1 Ultra芯片。

早在2015年,AMD在放弃芯片制造多年后,表示希望通过推出“小芯片”来夺回英特尔主导的服务器芯片市场。AMD高级副总裁塞缪尔·纳夫齐格(Samuel Naffziger) 在谈到公司当时的计划时称:“我们在芯片设计方面只有一颗子弹可以射中。”他指的就是Chiplet。

与将大量功能打包到一块大的硅片上不同,AMD选择将旗舰芯片分成四个独立的部分,并将它们拼接在一起。

“如果没有支持小芯片的技术,那么未来芯片的生产制造将变得过于昂贵,并且难以继续提供计算能力的飞跃。从长远来看,那些较旧的芯片设计也将消耗过多的功率,在经济上不可行。”一位资深业内人士告诉第一财经记者。

通过这种“小芯片”的设计思路,AMD降低了40%的制造成本。带来的直接好处是,AMD可以更加灵活地销售服务器芯片,根据需要添加和移除小芯片,并能针对不同的功能选项制定不同服务器芯片的价格区间。

开发Chiplet是AMD最成功的战略之一,并帮助AMD的收入从2015年的40亿美元增长到去年的164亿美元。

今年3月,英特尔、AMD、ARM、高通、台积电、三星、日月光等芯片厂商与Google 云、Meta、微软等科技巨头还共同成立了Chiplet标准联盟,正式推出了通用Chiplet的高速互联标准“UCIE”,旨在定义一个开放的、可互操作的标准,用于将多个Chiplet通过先进封装的形式组合到一个封装中。

在理想情况下,UCIE标准将允许芯片制造商混合和匹配使用不同制造工艺技术的芯片,并由不同公司制造成内置在单个封装内的产品。这意味着将美光制造的存储芯片、AMD制造的CPU芯片和高通制造的无线调制解调器将可以组装在一起,这将可以大大提高性能,同时节省大量电力。

业内人士对第一财经记者表示,这种通用互连的Chiplet要真正实现可能还需要几年时间。但不管怎样,这代表了未来芯片发展的一个方向。

行业挑战在哪儿?

根据研究机构Omdia的报告,到2024年,采用Chiplet处理器芯片的全球市场规模将达58亿美元,到2035年,这一规模有望达到570亿美元。Chiplet主要适用于大规模计算和异构计算,未来有望率先应用于数据中心应用处理器、自动驾驶等领域。

尽管市场前景充满想象,但也有部分公司对此技术路径保持谨慎态度。

“SOC(片上系统)做不了的,比如DRAM和XPU的集成,用Chiplet的设计正合适,现在关键的问题还是成本,所以目前的主要应用领域还是局限于高性能计算机。”一位国内从事Chiplet技术开发的企业负责人告诉第一财经记者。

英伟达副总裁伊恩·巴克(Ian Buck)则称,五年多前,英伟达遇到了光掩膜问题,也被称为标线限制(光掩膜无法打印大于850平方毫米的芯片),但该公司并没有选择Chiplet的解决方案。

部分原因是由于英伟达的GPU运行方式与CPU具有本质的不同。英伟达的芯片使用数千个计算内核一次执行大量相对简单的计算,为了在不采用“小芯片”方法的情况下应对光掩膜尺寸的限制,英伟达将精力集中在构建所谓的“超级芯片”上。

除了技术路径和原有赛道的偏离,对于国内厂商而言,发展Chiplet的挑战在于总体生态。

免责声明:上述内容仅代表发帖人个人观点,不构成本平台的任何投资建议。

- 冷血刺刀·2022-08-19好深奥啊!点赞举报

- XXX111·2022-08-18关注1举报