技术解析|智能驾驶和智能座舱 SoC 设计趋势

智能驾驶和智能座舱的复杂性不断提高,正在推动SoC设计进入一个新的发展阶段,如何通过新的集中式区域架构、集成AI技术的SoC设计,以及先进的接口IP(知识产权)技术,设计更好的SoC芯片。传统汽车电子系统通常基于单片SoC,这些SoC往往负责单一功能。

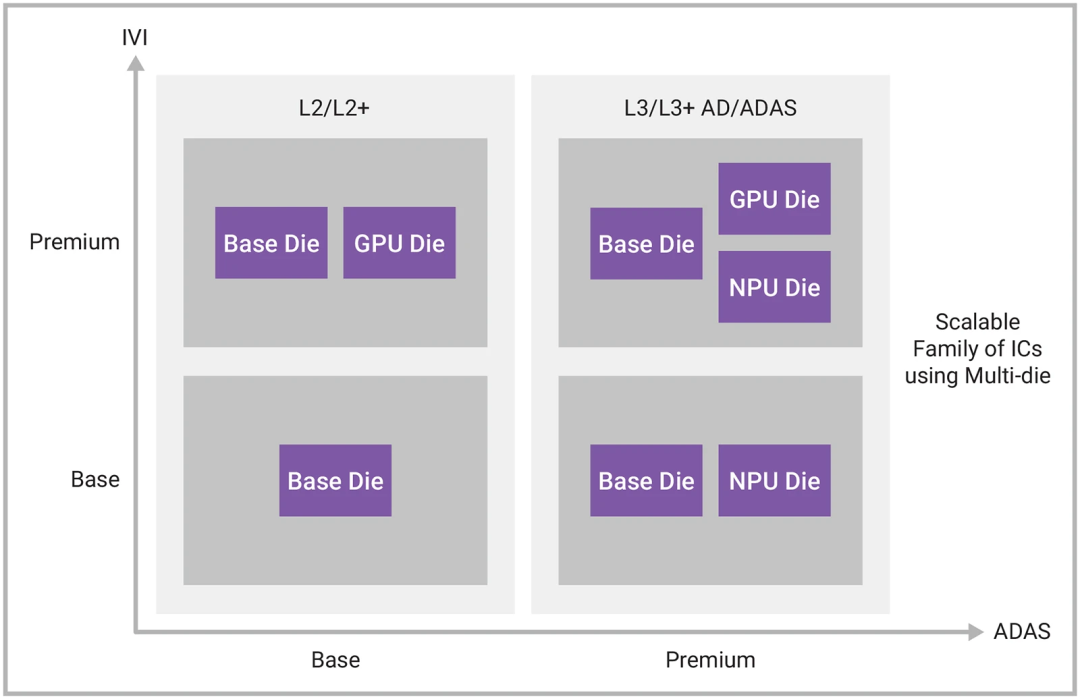

随着电动车辆的崛起及自动驾驶和车载娱乐系统的复杂化,单片SoC逐渐被多芯片设计所取代。在新的电子电气架构(EE架构)中,集中式计算模块成为核心,能够承担包括智能汽车的计算平台的多种应用。

Part 1

新型架构带来新的需求

这种架构的优势在于能够降低系统复杂性、提高扩展性并加速决策过程。

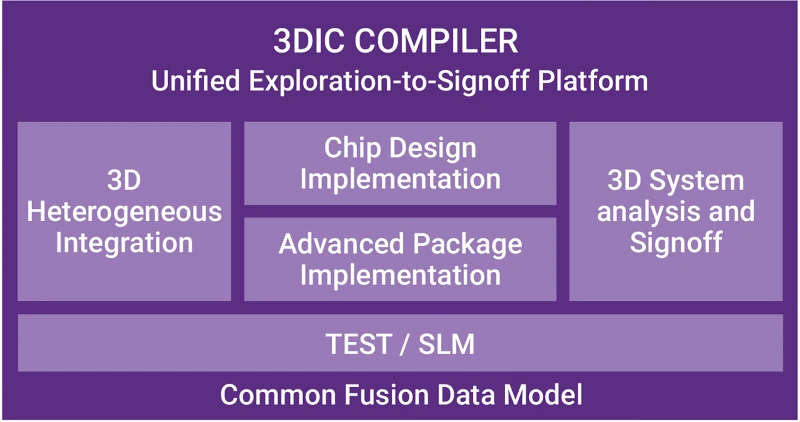

这些SoC通过先进的工艺技术实现高性能表现,并且在多芯片设计中,各种芯片以系统级封装(SiP)的形式集成,并通过Die-to-die连接实现协同工作。例如,在自动驾驶中央计算系统中,SoC可以包括多个芯片模块,如用于传感器接口、安全管理、内存控制和AI加速的芯片模块,并通过通用芯片互连接口(UCIe)实现互联。

UCIe是目前汽车SoC设计中最受关注的封装级通用互连标准。其定义和部署是由多个行业领导者共同推动的,最新的标准版本进一步增强了面向汽车用途的功能,如预测性故障分析和健康监测功能,并优化了封装成本。

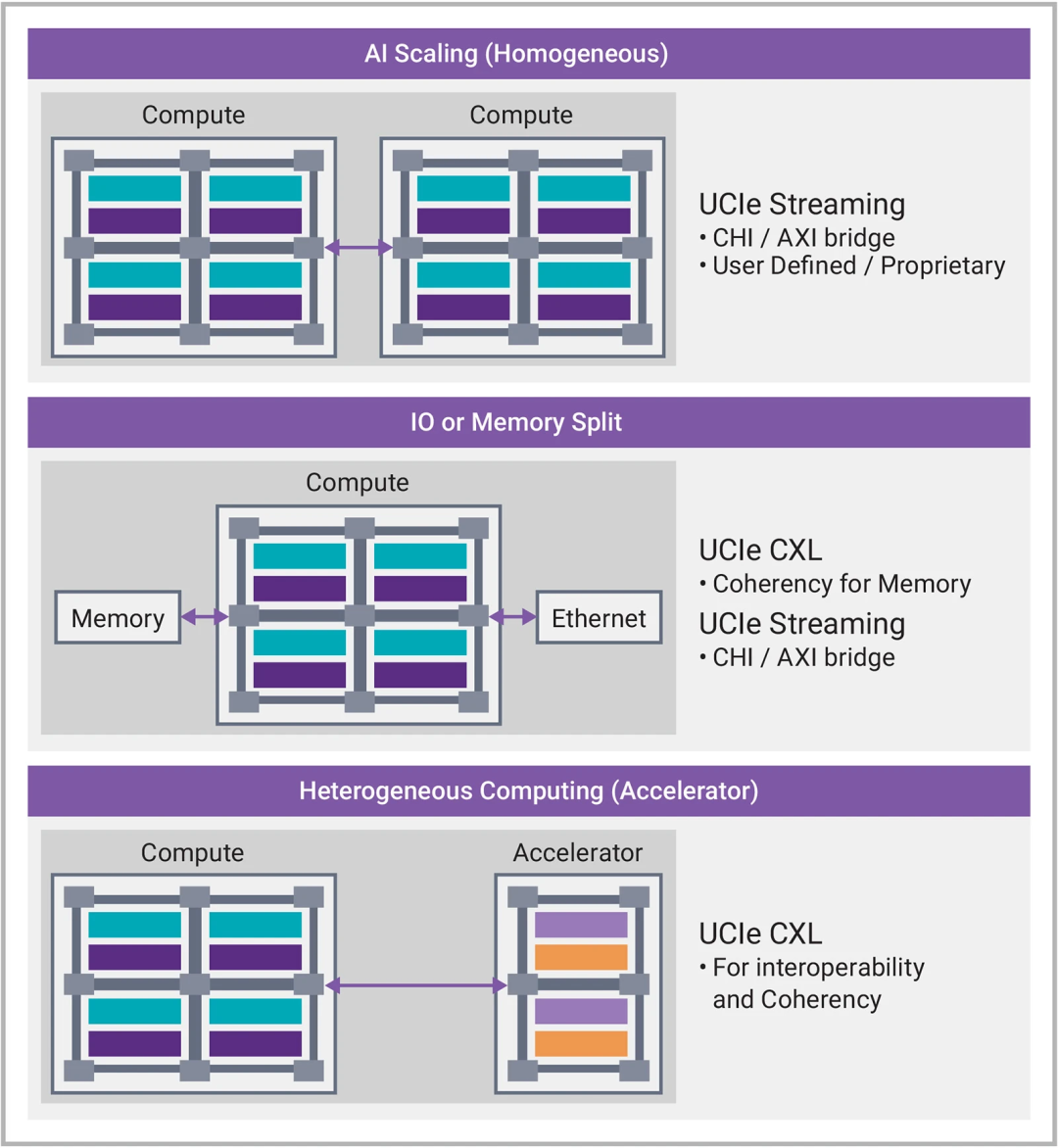

UCIe为ADAS和IVI SoC的设计带来了三大典型用例。

● 第一种是用于低延迟和一致性需求的场景,通常涉及两个片上网络(NoC)之间的连接。

● 第二种用例是将内存和I/O芯片通过CXL和UCIe协议连接到计算芯片,

● 而第三种则类似于高性能计算(HPC)的应用场景,通过UCIe连接AI加速器芯片与主CPU。

在这些用例中,UCIe所带来的关键优势在于延迟和功耗的优化。例如,Synopsys的UCIe IP通过Flit-Aware和Raw Die-to-Die接口优化延迟,使其在运行中能够适应不同的时钟域并实现最小化的传输延迟。

此外,UCIe的功率优化架构通过无源端接和可编程驱动强度等设计,进一步降低了芯片间的功耗。

Part 2

推动智能驾驶和智能驾驶舱体验

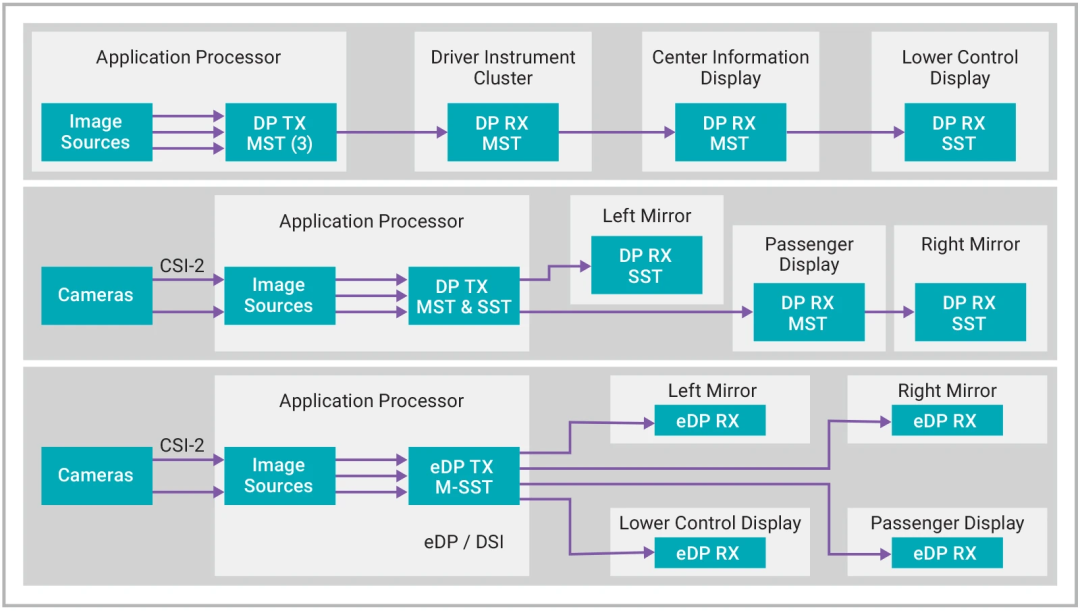

汽车制造商正通过高分辨率4K显示和多流传输(MTR)技术,为驾驶舱提供更具吸引力的用户体验。

在集中式区域架构下,IVI SoC通过菊花链显示拓扑,将单个GPU的图像传输至多个屏幕。菊花链设置不仅简化了汽车显示器的布线,还提升了用户体验的一致性。

IVI SoC设计中还引入了USB/DP接口的多功能集成应用,例如用于硅片生命周期管理、测试和调试的USB接口,可以在系统内部进行制造测试并支持固件的快速下载。

这些创新设计进一步强化了汽车显示系统的灵活性和可扩展性。软件定义汽车的出现,推动网络安全成为了汽车SoC设计中不可忽视的一环。

自2024年7月起,欧洲、日本和韩国的新车必须符合UNECE R155的网络安全法规,这意味着汽车OEM和供应商需要遵循ISO/SAE 21434标准,在E/E系统工程中加强网络安全流程。

汽车产业正处于向软件定义汽车转型的关键阶段,这一过程需要高度集成的系统架构和人工智能技术的结合,以满足日益复杂的用户需求和市场环境。

小结

集中式区域架构、多芯片设计、菊花链显示拓扑以及在单个SoC中集成ADAS和IVI功能,代表了汽车SoC设计的未来趋势。随着汽车技术的不断演进,更多创新将会涌现,从而推动智能化、安全化、可靠化的驾驶体验。

免责声明:上述内容仅代表发帖人个人观点,不构成本平台的任何投资建议。