消息称台积电成立团队规划建面板级封装mini line........

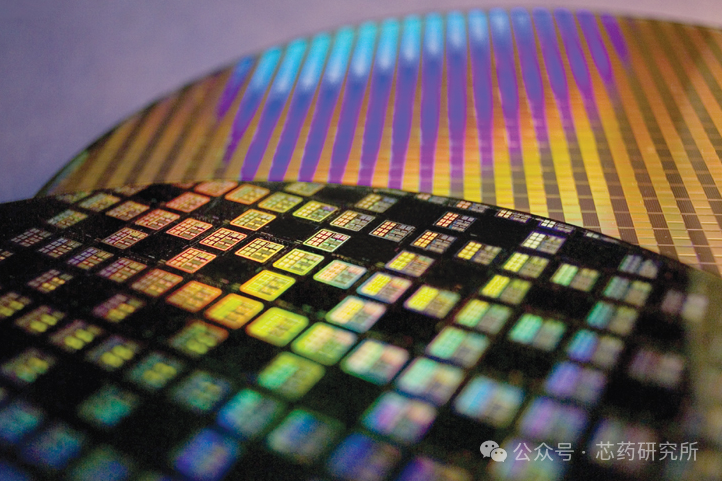

AI 等新应用爆发,先进封装话题持续火热,FOPLP(扇出型面板级封装)技术再度跃上台面。业界消息指出,晶圆代工龙头台积电正式成立团队,于“Pathfinding”阶段并规划建置mini line,以“方”代“圆”目标明确。

台积电2016年开发命名InFO(整合扇出型封装)的FOWLP(扇出型晶圆级封装)技术,用于iPhone7的A10处理器,之后封测厂便积极力推FOPLP方案,盼用更低生产成本吸引客户,但技术一直无法完全突破。目前终端应用仍停在成熟制程,如PMIC(电源管理IC)等产品。

不过业界消息传出,台积电想将先进封装技术从wafer level(晶圆级)转换到panel level(面板级)不再只是纸上谈兵,而是玩真的。主要规划采长宽各515与510毫米矩形基板,且现有正式团队研究,规划建置mini line。

他简单分析,台积电FOPLP可想像成矩形InFO,且多了低单位成本及大尺寸封装优势,整合台积电3D fabric平台其他技术,发展出2.5D / 3D等先进封装,以供高阶产品应用服务。可想像成矩形CoWoS,产品锁定AI GPU领域,客户是辉达。如进展顺利,2026~2027年或亮相。

AMD的FOPLP初期合作对象为日月光投控、力成,终端应用或用在PC或游戏机芯片。业界人士分析,过去PC、游戏机封装方式以FC-BGA为主,新品有可能升级到CoWoS等级。由于这类消费性产品成本敏感度高,IC设计厂商积极寻求更划算先进封装解决方案,最快2027年可看到产品上市。

半导体人士认为,早年FOPLP初期玩家只有力成、群创、日月光,又一路走走停停,拉货也是有一搭没一搭。为了正确投放资源,设备商投资较保守,主要是要大举更动规格满足客户,如今台积电正式加入,设备商态度也转向积极备战。

简言之,FOPLP生态链发展还是要看台积电,但产品定位,台积电持续掌握最高阶,封测厂吃中高阶以下市场。半导体人士认为,高速运算领域,三五年内CoWoS仍是主流,最领先3D封装SoIC也会在高阶领域大放异彩,这也是台积电的主战场。

对封测厂来说,最大利器即是产品升级并兼具成本效益,未来FOPLP是否能成功为新一代先进封装利器,要观察芯片厂商产品定位、翘曲等良率问题,以及整体性能价格是否让客户觉得值回票价。

来源:technews

免责声明:上述内容仅代表发帖人个人观点,不构成本平台的任何投资建议。